Why is the address offset shifted two places left in branch/jump operations in 32?bit RISC?like processors?

What will be an ideal response?

Typical processors have 32?bit, four?byte, instructions, yet the memory is byte addressed. That is, words have the

hexadecimal address 0,4,8,C,10,14 … However, the address bus can access addresses at any location; for example,

you can access address 0xABC3 (which is not word?aligned). Because the two lowest bits of an address are always

zero for an aligned address, there is no point in storing them when an address is stored in an instruction as an

offset; for example if the address offset is xxxxxxxx00, it is stored as xxxxxxxx. Consequently, when loaded it must

be shifted left by two places to generate xxxxxxxx00. Doing this extends the effective size of a literal by two bits.

You might also like to view...

A star has two ____.

A. points B. sides C. radii D. angles

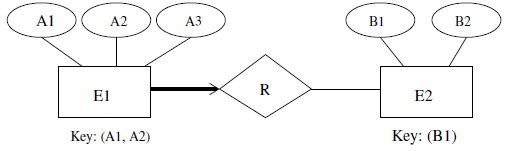

Translate the E-R diagram below into an SQL schema involving three tables: E1, R, and E2. Include all primary and foreign key constraints and assume all attributes have type integer.

(a)

(b) Add the following constraint to the above schema. Don't rewrite the whole schema; just

provide the material to be added and tell me where it goes.

(c) Create a view of this database that provides the values of A3 and B1 for all entities

related by R.

The each method automatically iterates once for each item stored in the array.

Answer the following statement true (T) or false (F)

The __________ IS is the information system that manages patients in surgery

a. Perioperative b. Registration c. Surgical d. None of the above