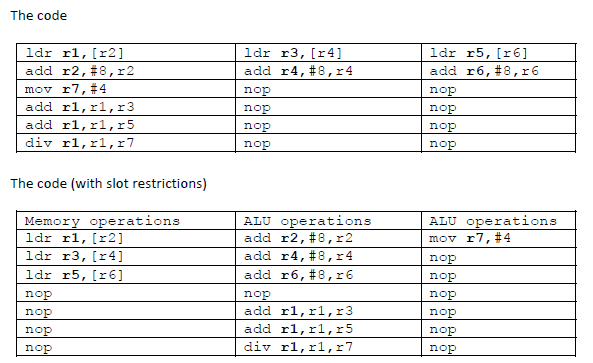

Demonstrate how a compiler might translate the following fragment of code into a form that can run on a VLIW processor that specifies three operations per instruction word (i.e., three instructions per bundle in Itanium terminology). You may perform instruction reordering. Assume that the latency for a load is three cycles and the latency for a multiply is two cycles (i.e., the load takes three cycles in total). Use a NOP whenever an instruction slot cannot be filled.

mov r7,#4

ldr r1,[r2]

ldr r3,[r4]

ldr r5,[r6]

add r1,r1,r3

add r1,r1,r5

div r1,r1,r7

add r2,#8,r2

add r4,#8,r4

add r6,#8,r6

Repeat the same exercise but assume that the VLIW processor can perform only one memory access operation

per cycle. Assume that the memory unit is fully pipelined; that is, it has a latency of three cycles but the next

memory operation can begin in the following cycle.

Computer Science & Information Technology

You might also like to view...

In a Microsoft domain using Kerberos authentication, after a client has been authenticated and received a TGT, the client presents this to a Ticket-Granting Service to receive something that allows authorization to resources for up to 8 hours. What is a common name for this last item?

A. timestamp B. password C. token D. smart card

Computer Science & Information Technology

The postfix representation of the prefix expression "-+*ABC/EF" is "AB*C+EF/-".

Answer the following statement true (T) or false (F)

Computer Science & Information Technology

Once a blend is created, changing the fill of the original objects will change the appearance of the blend.

Answer the following statement true (T) or false (F)

Computer Science & Information Technology

Describe three reasons why support organizations emphasize customer service.

What will be an ideal response?

Computer Science & Information Technology